磁致伸缩位移传感器利用FPGA的内部锁相环PLL可以将外时钟倍频成的高频、高稳定度、低抖动时钟,同样通过FPGA内部的PLL对倍频后的时钟进行相位内插,得到m路与倍频时钟同频的时钟,相位依次相差2π/m。磁致伸缩位移传感器测量时,在相同的Start信号下,通过这m个时钟的上升沿和下降沿分别开始计数,并通过这m个时钟的上升沿和下降沿分别对输入端口的Stop信号进行边沿捕获,在捕获到Stop信号边沿时,分别停止计数。相比于单一的时钟计数方法,这相当于在两个连续的参考时钟上升沿和下降沿内均插入了m-1个同频且相位均匀分布的时钟脉冲,将脉冲周期细成了2m等份。在不改变外部时钟频率的基础上,相当于把参考时钟频率进行了2m倍频。

即参考时钟频率为f,周期为T,计数器的计数值分别为n,则被测时间t可以表示为式3.4.

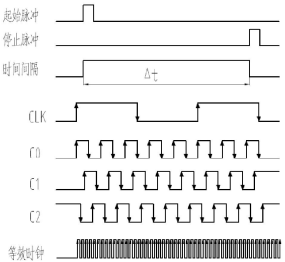

式中T为相移时钟计数法的等效时钟周期,fm为相移时钟计数法的等效计数频率。采用新的方法等效于将计数频率提高为原来的2m倍,相应的测量误差减小为原来的以3路时钟为例,输入时钟CLK经过FPGA的锁相环PLL倍频并移相之后,得到同频的3路时钟信号即C0、C1和C2,其相位依次相差120°,通过这3路时钟信号的上升沿和下降沿分别在相同的启动脉冲信号下开始计数,并在相同的停止脉冲信号下停止计数,磁致伸缩位移传感器计数原理如上图所示。

3路时钟的上升下降沿分别对起始脉冲信号和停止脉冲信号进行脉冲计数得到的计数值依次为N₁、N₂、N₃、N₄、N5、N₆,总的计数值N=N₁+N₂+N₃+N₄+N5+N₆,则测量时间为t=NT,测量精度为T=T/6.

微信扫一扫

微信扫一扫