1、SSI信号读取方案设计

SSI(SynchronousSerialInterface)全称是同步串行接口,全双工式工作方式,是一种带有数据帧同步的数据通信协议[1.主要应用在工业控制领域,尤其在高精度绝对值编码器传感器测量应用领域,作为一种实现较早的通信协议,许多国外公司都推出了具有SSI同步串行通信接口的绝对值编码测量传感器,例如美国的MTS公司RP型位移测量传感器,如图1所示,在测量控制领域,该位移传感器所采用的SSI协议相比于其他的通信协议,SSI协议具有接线简单,只需要四根传输线通信、传输速度快、采用差分方式传输抗干扰、高精度高分辨率的特点。

但通常具有SSI协议的传感器都没有现成匹配的数据读取设备,因此本文提出了利用CPLD和单片机来协同处理SSI数据,实现对SSI信号的读取。本文设计的SSI信号读取方案框图如图2.MTS位移传感器具有SSI信号输出端,SSI协议的CLK时钟信号和DATA数据信号为差分方式进行传输。

传输到“终端”后MAX490芯片将CLK、DATA差分信号转换成单端信号输入到CPLD中,CPLD中定义有脉冲时钟、逻辑控制等功能,数据在CPLD中由串行数据转换成并行数据,缓存起来等待单片机的读取,CPLD在单片机控制下,分批次每次并行八位读取数据,最后通过单片机的串口UART发送到上位机上处理分析。

2、CPLD 采集 SSI 信号

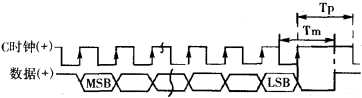

SSI信号是通过差分方式进行传输的,主要由同步差分时钟信号CLK+、CLK-和同步差分数据信号DATA+、DATA-,最后还有电源和地,这样传输最大的优点是信号传输过程中提高了抗干扰的能力,接线简单,系统的可靠性得到提高,如图3所示的是SSI的通信协议,T为脉冲时钟信号周期,tm为单稳态触发时间,tp为完整的数据帧之间的传输时间间隔。

当同步差分时钟信号与数据信号都保持在高电平状态时,为SSI通信的空闲时段;当SSI工作时,同步差分时钟信号开始有了脉冲,在第一个脉冲的下降沿阶段触发位移传感器中的编码器,其开始载入数据,其之后在时钟脉冲信号的上升沿编码器送出数据DATA,数据是以格雷码形式一位一位地传输,高位在前,低位在后,当传输完所有的数据位之后,时钟脉冲回到高电平,数据信号也相应回到高电平,一个数据帧传输结束。数据通过差分方式在线缆中传输,n是传输位数,传输位数有24、25、26位几种方式,实际使用25位传输方式。

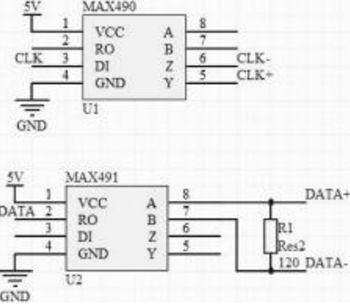

同步差分时钟信号与数据信号在位移传感器与CPLD之间是以差分形式传输的,而CPLD端口接受两者的信号为单端信号,所以需要应用差分平衡型收发合一芯片MAX490.将同步差分时钟信号CLK+、CLK-和同步差分数据信号DATA+、DATA-装换成单端信号,如图4所示是差分转单端的转换电路。

MAX490采用5V供电,内置有一个接收器和一个驱动器,驱动器输入端DI为CPLD的时钟脉冲信号CLK输入端,Z、Y分别是时钟脉冲信号的差分形式输出端,图4下半部分是DA-TA信号转换电路,接收器输出端RO连接CPLD的数据信号DATA,A、B端连接位移传感器的SSI输出,作为接收器的同相和反相输入端,差分数据信号DATA+、DATA-之间的R1电阻是接收器收入端匹配电阻,起到差分线路阻抗匹配的作用。

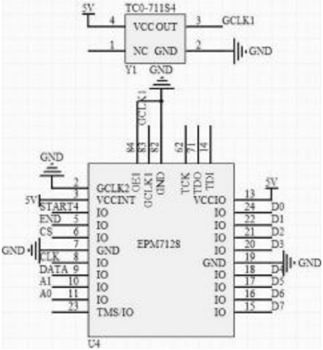

单端DATA信号由CPLD来采集,CPLD的功能有脉冲计数器、串行数据转并行数据寄存器、收发驱动器、输出控制等。如图5所示,所使用CPLD具有高阻抗、电可擦除等特点,可用门单元数2500个,宏单元数128个,输入输出线数84个,工作电压为5V。图中画出了部分所使用到的EPM7128管脚,未使用的已省略。TCO-711S4是由5V供电的有源晶体振荡器,相比无源晶振,可以给CPLD提供更加精确的GCLK1全局时钟信号,保证了逻辑时钟的准确度。CS为片选信号,由单片机给定选中CPLD工作就绪,START是脉冲时钟CLK开始信号,高电平时有效,END为所采集的25位数据并口转换结束完成状态指示,高电平是正在转换,低电平时转换完成,A1A0是地址译码,分别代表着四个8位数据的地址,由单片机控制地址译码来读取。脉冲时钟CLK是CPLD主时钟分频后得到250kHz的时钟脉冲后给传感器,脉冲时钟每发出一个时钟上升沿,传感器就会输出一个DATA数据。发送给传感器SSI通信时钟脉冲将25位数据DATA采集到并分批次转换成8位,缓存到内部定义的寄存器中,等待刷新和单片机的随时读取。CPLD中的脉冲时钟分频功能、串并转换功能、逻辑控制功能等在quartus中用Verilog描述这些硬件功能并调用Modelsim仿真结果,确定CPLD功能完好。

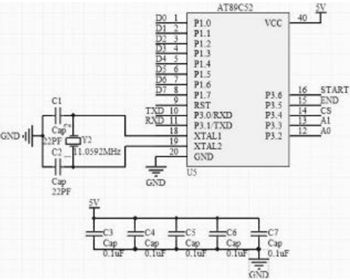

3、单片机并行读取

由单片机控制CPLD并行读取EPM7128相应寄存器中的数据,如图6所示是AT89C52并行读取CPLD寄存器中的数据电路图,单片机有5V供电,由五个0.1μF的非极性电容进行滤波,充当了电池的作用,使5V的电源更加稳定。单片机将P3.6口置高电平时,时钟脉冲CLK启动工作,P3.4口置CS为低电平时,CPLD开始采集转换数据,当END低电平时转换完成,P3.2和P3.3口控制A1A0地址,也就是CPLD中四个八位并行数据的地址,单片机每次读取八位数据,分四次将一帧数据读取完,A1A0地址为“11”时,单片机由DO~D7并口读取低八位数[];A1A0地址为“10”时,单片机读取次低八位数;A1A0地址为“01”时,单片机读取次高八位数;A1A0地址为“00”时,单片机读取次高八位数。

这样一帧数据就此读取完成,可在单片机里进行算法处理,为从串口的发送做准备。下面是有关单片机在程序中如何处理这4个字节数的算法部分代码回,其中unsignedint数据类型有SSIH和SSIL,unsignedlongint数据类型有SSIHH、SSIHHH:

j=SSIL&OxOf;//取低位数的低8位

k=(SSIL&OxfO)>>4;//取低位数的高8位

q=SSIH&OxOf;//取次低位数的低8位

h=(SSIH&OxfO)>>4;//取次低位数的高8位

b=SSIHH&OxOf;//取次高位数的低8位

d=(SSIHH&OxfO)>>4;//取次低位数的高8位

t=SSIHHH&OxOf;//取高位数的低8位

cm=(t*16777216+d*1048576+b*65536+h*4096+q*256+k*16+j);//十六进制数按照各权位转换成十进制

bm=cm;//cm赋值给bm

wei[0]=(bm/10000000)+0x30;

dm=bm%10000000;

wei[1]=(dm/1000000)+0x30;

fm=dm%1000000;

wei[2]=(fm/ 100000)+0x30;

hm=fm%100000;

wei[3]=(hm/ 10000)+0x30;

jm=hm%10000;

wei[4]=(jm/ 1000)+0x30;

lm=jm%1000;

wei[5]=(lm/ 100)+0x30;

nm=lm%100;

wei[6]=(nm/ 10)+0x30;

qm=nm%10;

wei[7]=qm+0x30;

把 bm拆分成8个字符数,存放到字符型数组里,之后就可以用串口发送函数将相对应的字符数组利用 for循环装载到 SBUF 寄存器中,通过串口发送到上位机上了。

4、结束语

经过整个系统性实验,成功地在上位机上显示了位移传感器的实测数值,实验结果说明了本文提出的各功能模块明确,技术方案可行。

微信扫一扫

微信扫一扫