0、引言

磁致伸缩性位移传感器是一种利用磁致伸缩原理来测量物体位移的高精度位置传感器,它将物体的位移量转换为时间量,通过测量时间量来测量位移,具有非接触测量、精度高、重复性好、稳定性可靠、适应性强等特点,目前在石油、化工、轧钢等行业得到了广泛的应用。

磁致伸缩性传感器输出的信号有多种输出方式,为了保证高精度、高位数数据传输可靠性,目前通常采用先进的同步串行接口输出技术(SSI)。由于单片机、DSP、工控机等工控领域常用的控制器一般不提供SSI接口,而市场上常见的SSI转换器多是将SSI信号转成通用异步串行信号,因此通信速率低、价格高、不易安装。

文中介绍一种基于FPGA/SOPC技术的嵌入式位移测量系统,能对多路磁致伸缩性传感器输出的SSI信号进行处理,并通过PCI/PMC总线实现与工业现场工控机的通信。

1、磁致伸缩性传感器工作原理及SSI信号

1∙1磁致伸缩性传感器工作原理

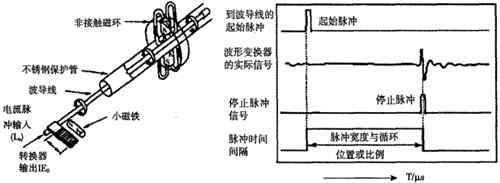

磁致伸缩型磁尺是利用Fe或Ni在磁场作用下具有伸缩能力的特性而设计的线性位移传感器。它由活动磁环和具有磁致伸缩性的波导管组成,活动磁环与波导管之间没有直接接触,它利用活动磁环产生的磁场与波导管内固定频率的电流产生的磁场相交,产生应变脉冲,该脉冲以固定速度运行到电子部件的测量头,从电流脉冲的上升沿到感应脉冲的上升沿之间的时间乘以这个固定速度,就是该活动磁环的准确位置,由此计算出的位移值由接口电路(SSI接口)提供给外部测量系统。传感器工作原理图如图1所示。

1∙2SSI接口协议

SSI接口,即同步串行接口,由一个传输时钟和一位数据组成。在空闲时间,传输时钟和数据都为高电平。数据高位先传,在时钟的第一个下降沿,接收端(从机)开始准备数据传输,随即在每个时钟的上升沿输出1位数据。1个数据字传输完毕以后,接收端(从机)将数据置为低电平,持续时间为tM,tM一般在15~35μs。如果在tM时间内时钟一直为高电平,那么接收端(从机)终止当前数据传输周期,为下一个重新开始的数据传输周期做好准备等待下一个时钟下降沿的到来;如果在tM时间内时钟出现了低电平接收端(从机)就会重发刚才发送的数据但是会在数据中多出一个0位来需要附加的一个时钟周期与之对应。

2、系统整体功能设计

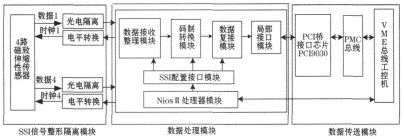

系统整体功能框图如图2所示整个磁致伸缩型传感器与工控机通信系统由3部分组成分别是SSI信号整形隔离模块、数据处理模块、数据传送模块。其中SSI信号整形隔离模块主要完成对4路磁致伸缩性传感器输出的SSI信号的整形、隔离以及电平转换;数据处理模块是整个多路数据采集系统的处理核心主要完成SSI信号数据的处理其中包括数据整理模块、码制转换模块、数据复接模块局部接口模块SSI配置接口模块和NiosⅡ嵌入式处理器模块整个数据处理模块是在FPGA芯片中实现的;第三部分为数据传送模块主要功能是通过桥接口芯片完成与工控机之间的数据传送。

系统整体功能如下:

(1)上位机通过NiosⅡ嵌入式处理器对整个FPGA数据采集系统进行监控负责系统数据分辨率、波特率、数据编码方式等工作参数以及启动、停止等运行控制参数的设置。

(2)FPGA芯片根据工作参数的设定对4路传感器数据进行检测发送不同波特率的时钟信号并接收传感器的差分数据对数据进行整理和变换最后将结果存放在存储器中。

(3)在NiosⅡ处理器的控制下上位机通过PCI9030桥接口芯片读取测量值。

3、系统硬件设计

系统硬件电路主要由4路磁致伸缩性磁尺、光电耦合器、电平转换芯片FPGA处理单元、PCI9030桥接口芯片、PMC总线几部分组成。其中FPGA是整个系统的核心器件。FPGA芯片选用Cyclone系列的EP1C12Q240C8芯片作为该系统的控制芯片[3]。光电耦合器选用高速光耦HCPL2631.

系统设计的硬件板卡是以工控机的VME总线为母板通过PMC总线集成到上位机控制系统中。所以设计的转速采集卡应遵循PMC卡的设计规范。PMC总线是连接VME64x板、CompactPCI等板的一种子板结构采用PCI标准的电气层和逻辑层的定义兼容PCI总线标准电气性能也与之兼容[4]。

PCI9030是一种为扩展适配卡而推出的高性能目标接口芯片[5]系统硬件设计中PCI9030芯片PCI一侧的相应引脚与PMC总线的相应引脚相连局部总线一侧与FPGA相连通过设置9030内部寄存器的值可以将PMC总线的各种操作(包括读写等功能)转换为局部地址空间的操作从而实现FPGA芯片与PMC总线之间的数据传送。

4、系统软件设计

数据整理模块是整个系统的核心部分它是在FPGA中完全通过软件实现的模块功能。整个模块包括5个子模块分别为数据接收整理模块、码制转换模块、数据复接模块、局部接口模块和NiosⅡ嵌入式处理器模块。整个软件系统选用了Quar-tusⅡ软件系统提供的集成化文本编辑程序实现并应用VHDL硬件描述语言进行设计输入。

4∙1NiosⅡ嵌入式处理器模块

SOPC系统是整个多路数据采集系统软件部分的控制中心负责处理与工控机的通讯协议以及配置多路数据采集系统的工作模式和工作参数。SOPC通过RS-232接口与计算机交互通过自定义部件实现对系统逻辑的运控和管理。设计中SOPC系统包含NiosII软核、BRAM、EPCS控制器、RS-232控制器、自定义的SSI寄存器接口部件以及系统互联部分。

多路数据采集卡上电复位以后SOPC系统软件首先执行系统初始化然后根据设计要求可以同时设置波特率、数据分辨率、编码方式、工作模式以及运行控制等任务。

多路数据采集卡没有外置的通用存储器设备这样SOPC软件必须在FPGA内部运行因此占用了FPGA内部嵌入式的RAM块但是应用这种设计方法可以简化外围电路设计提高系统的集成度和可靠性软件运行效率高。

4∙2数据接收整理模块

数据接收整理模块在NiosⅡ嵌入式处理器的控制下发送特定波特率的时钟然后接收传感器输出的位移数据数据格式符合SSI接口协议。数据接收整理模块根据控制器输入的数据字位宽接收串行数据同时实现数据的串并转换。在接收完一个完整的数据字后进入空闲时间等待下一个数据传输周期。根据SSI接口协议空闲时间可以设置为≥35μs。根据输入的波特率选择可以得出最短的空闲时间。

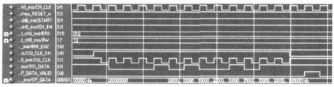

数据接收模块的ModelSim仿真波形如图3所示。仿真图中设置波特率为500K数据编码方式为格雷码第一路SSI编码器的数据字有效位宽为12bit输出的二进制数据为0x14d。

4∙3码制转换模块

码制转换模块根据输入的编码方式选择进行码制转换。如果采用格雷码编码,那么将输入的格雷码转换为二进制;如果采用二进制编码,则不进行码制转换,直接输出输入的二进制码。码制转换模块的输入信号来自于数据接收模块的输出信号。格雷码(GrayCode,简称G码)是典型的循环码,特点是序号相邻的两组代码只有一位码不同(包括头尾两组代码),且具有循环性。格雷码的这种特点有助于提高电路的可靠性。

4∙4数据复接模块

数据复接模块接收4路传感器输出的数据,并对每路数据组帧以后输入数据缓存(FIFO)中。每路SSI通道的数据帧格式为:数据帧帧头+32位SSI通道数据。其中第一路SSI通道数据帧帧头定义为0xFFFFFFF0;第二路SSI通道数据帧帧头定义为0xFFFFFFF3;第三路SSI通道数据帧帧头定义为0xFFFFFFF5;第四路SSI通道数据帧帧头定义为0xFFFFFFF9.

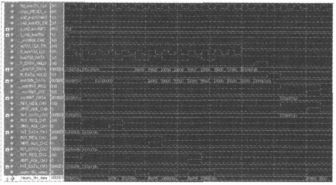

数据复接模块的ModelSim仿真波形如图4所示。仿真条件为波特率为500K,数据编码方式为格雷码,仿真图中第一路磁致传感器的数据字有效位宽为12-bit,输出的二进制数据为0x18d,其余3路的数据字有效位宽为32-bit,输出的二进制数据为0x0fc,仿真结果正确。

4∙5局部总线接口模块

局部总线接口模块是实现FPGA内部功能模块与局部总线进行数据交换的接口模块,基本功能是实现读数据操作,即将数据复接模块输出的每路SSI数据帧读入到PCI9030局部总线侧,实现和PMC总线即工控机之间的数据交换。由于SSI接口的时钟和PCILocal接口的时钟不一致,因此为了能实现数据的传输,将数据复接模块输出的数据帧进行了数据缓存,使用异步FIFO存储器作为数据缓存,这样由异步FIFO存储器配合PCILocal接口逻辑,实现了SSI数据帧与PMC总线之间的数据传输。

局部读写操作接口模块用状态机实现,一次读(写)操作包含4个总线操作状态:空闲状态(idle)、地址态(address)、数据/等待态(data/wait)和恢复态(recovery)。

4∙6SSI配置接口模块

SSI配置接口模块包含针对系统以及SSI接口的命令和控制寄存器,用于系统控制运行以及系统管理配置。SOPC系统通过Avalon总线接口访问SSI配置接口模块内部的命令和控制寄存器,达到系统运控管理功能。

5、系统测试结果及分析

整个系统硬件连接正确后,就可以对系统进行整体测试。在实验室条件下,对采集卡单路数据的采集、处理与传输过程进行验证,采用SSI接口的磁致伸缩性传感器作为外部数据输入,该传感器用外部24V电源供电,输出为格雷码,分辨率为12bit,其余3路为内部由软件产生的数据源。经显示软件可得出正确的绝对位置与时间的关系曲线如图5所示。第1路为外部信号源输入,其余3路均为内部信号源输入。

6、结束语

设计了基于NiosⅡ处理器的嵌入式多通道磁致伸缩性传感器数据采集、通信系统。系统主要选择FPGA作为核心处理器,并配置有PCI9030作为FPGA与PMC总线的数据传输通道。整个设计的创新点在于应用嵌入式技术实现了数据的采集与传输,并且在此硬件平台基础上完成对输入输出信号的处理与存储。

该系统可以推广到前端端口为SSI接口的绝对编码器或其他传感器的测量系统中,能满足不同工业现场测量的要求。整个设计系统即简化了系统电路,又降低了成本,器件性能稳定,因此可广泛应用于各种工业现场。

微信扫一扫

微信扫一扫