1、概述

磁致伸缩位移传感器(MagnetostrictivePosi-tionSensor)是利用两个不同磁场相交时产生的应变脉冲信号被检测到的时间来计算出磁场相交点的准确位置,具有高精度、高响应、低迟滞、高可靠性、非接触、寿命长、稳定性高、安装方便等优点,无须重新标定,无须定期维护,因而被广泛应用于机器人、自动化技术、探测与开发技术、试验机与试验技术等精确测量领域。

本文介绍一种基于SSI接口的磁致伸缩位移传感器,并结合EDA技术设计了一种位移测量系统,能够实现多路SSI信号输出,并可以通过PCI总线传输接口实现与上位机的通信。磁致伸缩传感器采用非接触测量运动物体的直线位移,具有电压输出、电流输出、SSI和现场总线等多种输出方式。为了满足高精度测量和可靠性传输,本文采用具有很高抗干扰性的SSI同步串行接口(Synchronous SerialInterface)输出方式,可以远距离传送数据以同步方式进行交换。随着EDA技术的发展,用基于现场可编程门阵列FPGA的数字采集系统对传感器进行控制,为实现数字化传感器的控制提供了一种新的有效方法。

2、SSI通信原理

SSI通信协议是一种同步串行接口协议,通信中只涉及两条信号线,即同步时钟信号和数据信号,数据可以通过24/25/26位编码模式串行传输到控制系统中。SSI接口的磁致伸缩传感器采用差分同步时钟信号C+、C-和差分数据信号D+、D-[1]。通过差分传输方式可以有效地提高信号的抗干扰能力,增加了系统控制的可靠性。由于SSI接口的设备传输速率比较高,而单片机和DSP等很难实现高速信号的采集,而且一般的工控机也不具有SSI接口[2],所以采用FPGA进行测量系统设计,通过其内部丰富的逻辑资源实现数据的采集。

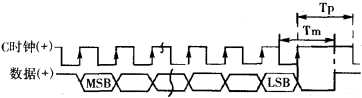

SSI信号传输时序图如上图所示,其中MSB为最高位,LSB为最低位,Tm为单稳态触发时间,Tp为两个数据传输间隔时间。

3、测量系统总体设计

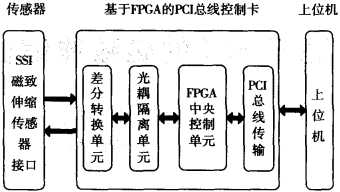

本文采用FPGA实现SSI接口磁致伸缩位移传感器的测量,并结合差分转换、光耦隔离和PCI总线数据传输构成基于FPGA数据采集系统。通过上位机软件自动控制,监控传感器产生的位移信号,并可以进行后续分析处理。测量系统的原理框图如下图所示。

3.1系统实现

基于FPGA的PCI总线控制卡主要包括4个传感器基于FPGA的PCI总线控制卡上位机部分:差分转换单元、光耦隔离单元、FPGA中央控制单元和PCI总线传输单元。

(1)差分转换单元

由于SSI时钟信号输入端和数据信号输出端为差分信号,需要采用差分驱动器和差分接收器进行差分转换。对于单路SSI接口,可以采用同时具有接收和发送功能的TI公司的SN75179进行转换;对于多路SSI接口,可以在设计中采用多个4路差动驱动器SN75173和4路差动接收器SN75174进行转换。

(2)光耦隔离单元

为了保证SSI信号的高速可靠传输,设计中采用对输入和输出电信号有良好隔离作用的高速光耦合器6N137.通过光耦隔离可以得到干扰小、稳定性强的数据信号,并将其传输到FPGA。

(3)FPGA中央控制单元

FPGA中央控制器设计了一个闭环的控制系统,实现SSI的同步数据采集和PCI总线传输。首先上位机给定初始信号和SSI数据开始采集信号,FPGA产生一个时钟脉冲信号,SSI磁致伸缩传感器在FPGA发出时钟脉冲信号的控制下,开始一位位发送串行数据到FPGA控制器,FPGA通过串并转换将SSI的数据信号转换成可供PCI总线接收的并行数据,通过PCI接口传输到上位机,进行后续处理。

(4)PCI总线传输单元

为满足PCI总线接口规范,选用了PCI9052专用接口芯片,它支持位移测量控制卡的即插即用和自动配置等功能,并提供DMA数据传输方式。通过上位机发送采集命令,接收FPGA中央控制单元传输数据,传输到上位机。

3.2SSI的时序设计

根据SSI通信协议,接收和发送信号的双方在时钟脉冲信号的控制下,从最高有效位开始同步传输数据。接收过程如下:FPGA控制器根据时钟信号的第一个下降沿,单稳态电路被激活,SSI数据信号开始准备传输;当第一个时钟上升沿到来时,第一位数据开始传输,随即时钟信号处于下降沿,单稳态电路再次被激活;接着,FPGA通过时钟信号对串行数据进行一位位地接收,并将串行数据转化成并行数据;时钟信号末端,控制器获得最低有效位数据,

时钟脉冲信号停止,经过单稳态时间(Tm)数据信号转向高电平,数据传输停止,单稳态电路不被激活;FPGA控制器接收完一个完整的数据字后,进入到空闲时间,等待下一个数据传输周期。串行数据转化完并行数据后锁存,等待上位机读取。

上图中,CLK为系统时钟,CLOCK为SSI的输入时钟,DIN为SSI的数据输出,out为串并转换移位寄存器数据,DOUT为转换完成的数据锁存器,READ为锁存器控制信号。当CLOCK时钟信号开始工作,FPGA控制器开始读取SSI数据信号,并进行串并转换。当READ信号有效,上位机通过PCI总线读取SSI数据信号,分析证明整个系统下载到FPGA后运行良好。

4、结束语

本文根据磁致伸缩传感器的工作原理和SSI通信协议,设计了一种基于FPGA的SSI磁致伸缩传感器位移测量系统,实现了SSI的位移信号的采集。通过FPGA综合管理和时序设计,并经过PCI总线传输SSI信号到上位机进行后续处理。仿真结果证明系统有良好的稳定性和传输可靠性。通过单路SSI的设计,可以扩展为多路SSI位移控制,实现大型试验机或者设备的位移测量,具有广泛的应用性。

微信扫一扫

微信扫一扫